# **CMX138A** Audio Scrambler and Sub-Audio Signalling Processor

D/138A/4 October 2014

## CMX138A: Audio Scrambler and Sub-Audio Signalling Processor with Auxiliary System Clock, ADC and DAC for use in Analogue Radio Systems

## Features

- Programmable Audio Scrambler

- Concurrent Audio/Signalling Operations

- Full Audio-band Processing: Pre and De-emphasis, Compandor, Scrambler and Selectable 2.55/3 kHz Filters

- Auxiliary ADC and Auxiliary DAC

- C-BUS Serial Interface to Host µController

- Two Analogue Inputs (Mic or Discriminator)

- Selectable Audio Processing Order

- Sub-audio Signalling: CTCSS, DCS

- Auxiliary System Clock Output

- Tx Output for Single-point Modulation

- Low-power (3.0V to 3.6V) Operation

- Flexible Powersave Modes

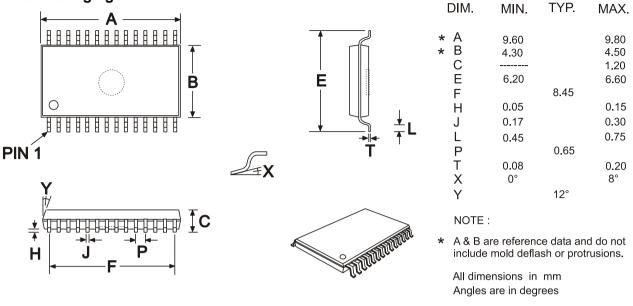

- Available in 28-pin TSSOP Package

## **1** Brief Description

The CMX138A is a half-duplex, audio scrambler and sub-audio signalling processor IC for Analogue Twoway Radio applications. This makes it a suitable device for the leisure radio markets (FRS, MURS, PMR446 and GMRS).

This device provides a user programmable frequency inversion audio scrambler, companding and pre/deemphasis – performing simultaneous processing of Sub-audio and In-band signalling.

Other features include an auxiliary ADC channel and an auxiliary DAC interface (with optional RAMDAC, to facilitate transmitter power ramping).

The device has flexible powersaving modes and is available in a 28-pin (E1) TSSOP package.

## CONTENTS

| Secti | ion        | <u> </u>                                        | Page |  |  |  |  |  |  |

|-------|------------|-------------------------------------------------|------|--|--|--|--|--|--|

| 1     | Brief Desc | ription                                         | 1    |  |  |  |  |  |  |

| 2     | History5   |                                                 |      |  |  |  |  |  |  |

| 3     | Block Diad | gram                                            | 6    |  |  |  |  |  |  |

|       | -          | -                                               |      |  |  |  |  |  |  |

| 4     |            | t<br>gnal Definitions                           |      |  |  |  |  |  |  |

| 5     | External C | components                                      | 9    |  |  |  |  |  |  |

| Ŭ     |            | B Layout Guidelines and Power Supply Decoupling |      |  |  |  |  |  |  |

| 6     |            | escription                                      |      |  |  |  |  |  |  |

|       |            | •                                               |      |  |  |  |  |  |  |

| 7     |            | escriptions                                     |      |  |  |  |  |  |  |

|       |            | al Frequency                                    |      |  |  |  |  |  |  |

|       |            | st Interface                                    |      |  |  |  |  |  |  |

|       | 7.2.1      | C-BUS Operation                                 |      |  |  |  |  |  |  |

|       |            | vice Control                                    |      |  |  |  |  |  |  |

|       | 7.3.1      | Signal Routing                                  |      |  |  |  |  |  |  |

|       | 7.3.2      | Mode Control                                    |      |  |  |  |  |  |  |

|       | 7.4 Au     | dio Functions                                   |      |  |  |  |  |  |  |

|       | 7.4.1      | Audio Receive Mode                              | 17   |  |  |  |  |  |  |

|       | 7.4.2      | Audio Transmit Mode                             | 19   |  |  |  |  |  |  |

|       | 7.4.3      | Audio Compandor                                 | 23   |  |  |  |  |  |  |

|       | 7.5 Su     | b-audio Signalling                              | 25   |  |  |  |  |  |  |

|       | 7.5.1      | Receiving and Decoding CTCSS Tones              | 27   |  |  |  |  |  |  |

|       | 7.5.2      | Receiving and Decoding DCS Codes                | 28   |  |  |  |  |  |  |

|       | 7.5.3      | Transmit CTCSS Tone                             | 30   |  |  |  |  |  |  |

|       | 7.5.4      | Transmit DCS Code                               | 30   |  |  |  |  |  |  |

|       | 7.6 In-    | band Signalling – User Tones                    | 30   |  |  |  |  |  |  |

|       | 7.6.1      | Receiving and Decoding In-band Tone             |      |  |  |  |  |  |  |

|       | 7.6.2      | Transmitting In-band Tone                       |      |  |  |  |  |  |  |

|       | 7.7 Au     | xiliary ADC Operation                           |      |  |  |  |  |  |  |

|       |            | xiliary DAC/RAMDAC Operation                    |      |  |  |  |  |  |  |

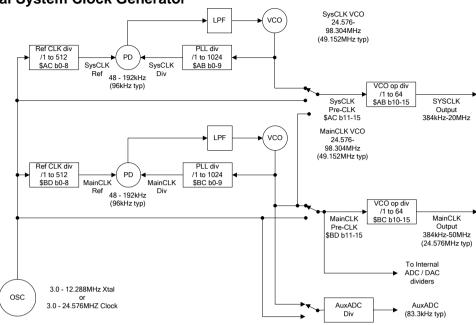

|       |            | gital System Clock Generator                    |      |  |  |  |  |  |  |

|       | 7.9.1      | Main Clock Operation                            |      |  |  |  |  |  |  |

|       | 7.9.2      | System Clock Operation                          |      |  |  |  |  |  |  |

|       | -          | PIO                                             |      |  |  |  |  |  |  |

|       |            | gnal Level Optimisation                         |      |  |  |  |  |  |  |

|       | -          | Transmit Path Levels                            |      |  |  |  |  |  |  |

|       |            | Receive Path Levels                             |      |  |  |  |  |  |  |

| •     |            |                                                 |      |  |  |  |  |  |  |

| 8     |            | gister Summary                                  |      |  |  |  |  |  |  |

|       | 8.1.1      | Interrupt Operation                             |      |  |  |  |  |  |  |

|       | 8.1.2      | General Notes                                   | 36   |  |  |  |  |  |  |

| 9     | Configurat | tion Guide                                      | 37   |  |  |  |  |  |  |

|       |            |                                                 |      |  |  |  |  |  |  |

|    | 9.1  | C-E     | BUS Register Details                                |    |  |  |  |  |  |  |

|----|------|---------|-----------------------------------------------------|----|--|--|--|--|--|--|

|    |      | 9.1.1   | Reset Operations                                    |    |  |  |  |  |  |  |

|    |      | 9.1.2   | General Reset - \$01 write                          |    |  |  |  |  |  |  |

|    |      | 9.1.3   | AuxADC and TX MOD Mode - \$A7 write                 | 40 |  |  |  |  |  |  |

|    |      | 9.1.4   |                                                     |    |  |  |  |  |  |  |

|    |      | 9.1.5   | AuxADC Data - \$A9 read                             | 41 |  |  |  |  |  |  |

|    |      | 9.1.6   | System Clk PLL Data - \$AB write                    | 42 |  |  |  |  |  |  |

|    |      | 9.1.7   | System Clk REF - \$AC write                         | 42 |  |  |  |  |  |  |

|    |      | 9.1.8   | Analogue Input Gain - \$B0 write                    | 43 |  |  |  |  |  |  |

|    |      | 9.1.9   | Analogue Output Gain - \$B1 write                   |    |  |  |  |  |  |  |

|    |      | 9.1.10  | AuxADC Threshold Data - \$B5 write                  | 45 |  |  |  |  |  |  |

|    |      | 9.1.11  | Power Down Control - \$C0 write                     | 45 |  |  |  |  |  |  |

|    |      | 9.1.12  | Mode Control – \$C1 write                           |    |  |  |  |  |  |  |

|    |      | 9.1.13  | Audio Control – \$C2 write                          |    |  |  |  |  |  |  |

|    |      | 9.1.14  | Tx In-band Tone - \$C3 write                        |    |  |  |  |  |  |  |

|    |      | 9.1.15  | Status – \$C6 read                                  |    |  |  |  |  |  |  |

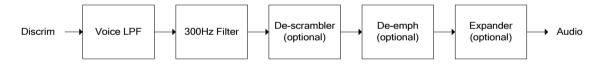

|    |      | 9.1.16  | Programming – \$C8 write                            |    |  |  |  |  |  |  |

|    |      | 9.1.17  | Scrambler Inversion Frequency – \$CB write          |    |  |  |  |  |  |  |

|    |      | 9.1.18  | Tone Status - \$CC read                             | 48 |  |  |  |  |  |  |

|    |      | 9.1.19  | Audio Tone - \$CD: 16-bit write                     | 49 |  |  |  |  |  |  |

|    |      | 9.1.20  | Interrupt Mask - \$CE write                         |    |  |  |  |  |  |  |

|    |      | 9.1.21  | Reserved - \$CF write                               |    |  |  |  |  |  |  |

|    | 9.2  | Pro     | ogramming Register Operation                        | 53 |  |  |  |  |  |  |

|    |      | 9.2.1   | Program Block 0 – reserved                          | 54 |  |  |  |  |  |  |

|    |      | 9.2.2   | Program Block 1 – In-band Tone Setup:               | 54 |  |  |  |  |  |  |

|    |      | 9.2.3   | Program Block 2 – CTCSS and DCS Setup               | 55 |  |  |  |  |  |  |

|    |      | 9.2.4   | Program Block 3 – AuxDAC, RAMDAC and Clock Control: | 57 |  |  |  |  |  |  |

|    |      | 9.2.5   | Program Block 4 – Gain and Offset Setup:            | 58 |  |  |  |  |  |  |

|    |      | 9.2.6   | Initialisation of the Programming Register Blocks:  | 62 |  |  |  |  |  |  |

| 10 | App  | licatio | n Notes                                             |    |  |  |  |  |  |  |

|    | • •  |         |                                                     |    |  |  |  |  |  |  |

| 11 |      |         | ce Specification                                    |    |  |  |  |  |  |  |

|    | 11.1 |         | ctrical Performance                                 |    |  |  |  |  |  |  |

|    |      |         | Absolute Maximum Ratings                            |    |  |  |  |  |  |  |

|    |      |         | Operating Limits                                    |    |  |  |  |  |  |  |

|    |      |         | Operating Characteristics                           |    |  |  |  |  |  |  |

|    |      |         | Parametric Performance                              |    |  |  |  |  |  |  |

|    | 11.2 | -       | 3US Timing                                          |    |  |  |  |  |  |  |

|    | 11.3 | o Pac   | ckaging                                             |    |  |  |  |  |  |  |

## <u>Table</u>

#### <u>Page</u>

| Table 1 Definition of Power Supply and Reference Voltages | 0 |

|-----------------------------------------------------------|---|

|                                                           |   |

| Table 2 Xtal/clock Frequency Settings for Program Block 3 |   |

| Table 3 DCS Codes and CTCSS Tones                         |   |

| Table 4 DCS Modulation Modes                              |   |

| Table 5 DCS 23 Bit Codes                                  |   |

| Table 6 In-band Tone                                      |   |

|                                                           |   |

#### $\ensuremath{\textcircled{}^{\circ}}$ 2014 CML Microsystems PIc

| Table 7 C-BUS Registers          | 35   |

|----------------------------------|------|

| Table 8 Reset Operations         | 38   |

| Table 9 Voice Level Attenuation  | 50   |

| Table 10 Voice Level Attenuation | 50   |

| Table 11 RAMDAC Values           | 57   |

| Table 12 Voice Level Attenuation | . 59 |

## Figure

#### Page

| Figure 1 Block Diagram                                        | 6  |

|---------------------------------------------------------------|----|

| Figure 2 CMX138A Recommended External Components              | 9  |

| Figure 3 CMX138A Power Supply Connections and De-coupling     | 11 |

| Figure 4 C-BUS Transactions                                   |    |

| Figure 5 Signal Routing                                       |    |

| Figure 6 Rx 25kHz Channel Audio Filter Frequency Response     |    |

| Figure 7 De-emphasis Curve for TIA/EIA-603 Compliance         |    |

| Figure 8 Tx Channel Audio Filter Response and Template (ETSI) |    |

| Figure 9 Tx Channel Audio Filter Response and Template (TIA)  |    |

| Figure 10 Audio Frequency Pre-emphasis                        | 21 |

| Figure 11 Expandor Transient Response                         | 23 |

| Figure 12 Compressor Transient Response                       | 24 |

| Figure 13 Low Pass Sub-audio Band Filter for CTCSS and DCS    |    |

| Figure 14 AuxADC IRQ Operation                                |    |

| Figure 15 Digital Clock Generation Schemes                    |    |

| Figure 16 Default Tx Audio Filter Line-up                     |    |

| Figure 17 Default Rx Audio Filter Line-up                     |    |

| Figure 18 C-BUS Timing                                        |    |

| Figure 19 Mechanical Outline of 28-pin TSSOP (E1)             | 73 |

|                                                               |    |

It is always recommended that you check for the latest product datasheet version from the CML website: [www.cmlmicro.com].

# 2 History

| Version | Changes                                                                                                                                                                                                                                                                                                                                                                    | Date     |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4       | Updated CTCSS detector response times, following product characterisation.<br>Added note 74 about statistical processes.                                                                                                                                                                                                                                                   | Oct 2014 |

| 3       | <ul> <li>Added description of fine attenuation settings to \$CD and P4.2, P4.3</li> <li>Note that it is possible to alter standard CTCSS settings when in Tx mode, but not custom settings or DCS settings</li> <li>Update MOD and AUDIO output drive parameters, after characterisation</li> <li>Correct minor typos and change document status to full issue.</li> </ul> | Dec 2012 |

| 2       | <ul> <li>Enhanced description of C-BUS latency time, just before Fig 4.</li> <li>Correction to Audio Tone (\$CD) register, code 1100<sub>b</sub>, section 9.1.19.</li> <li>Correction to Program Block 4, registers P4.10 and P4.11, section 9.2.5.</li> </ul>                                                                                                             | Nov 2010 |

| 1       | First Issue of CMX138A                                                                                                                                                                                                                                                                                                                                                     | Jun 2010 |

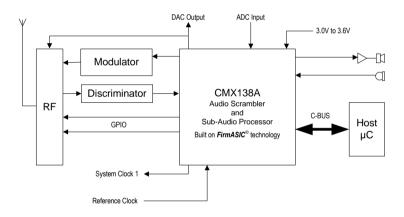

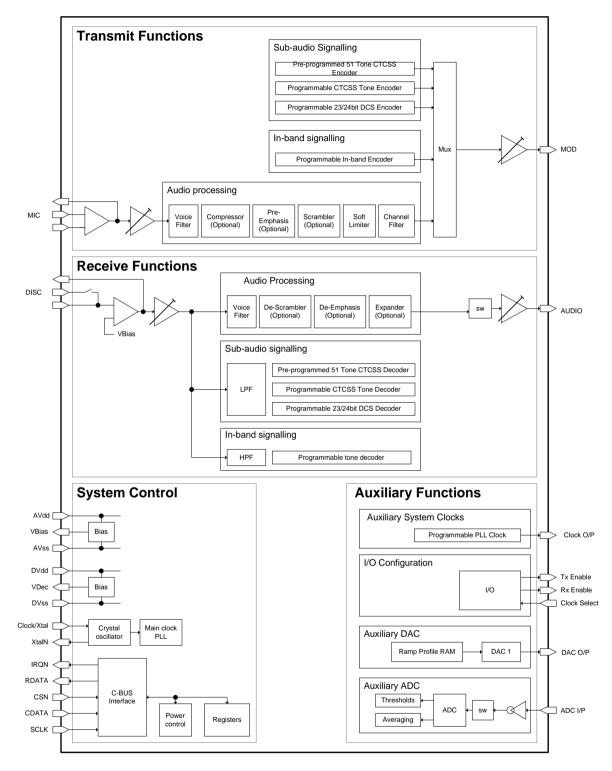

# 3 Block Diagram

# 4 Signal List

| CMX138A | Signal<br>Name | Туре  | Description                                                                                                                                                                                                                                                  |  |  |

|---------|----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | TXENA          | OP    | Digital output pin – TxENA (active low).                                                                                                                                                                                                                     |  |  |

| 2       | VDEC           | PWR   | Internally generated 2.5V digital supply voltage. Must be decoupled to DVSS by capacitors mounted close to the device pins. No other connections allowed.                                                                                                    |  |  |

| 3       | SYSCLK         | OP    | Synthesised digital system clock output.                                                                                                                                                                                                                     |  |  |

| 4       | IRQN           | OP    | C-BUS: A 'wire-ORable' output for connection to the Interrupt Request<br>input of the host. Pulled down to DVSS when active and is high<br>impedance when inactive. An external pull-up resistor is required.                                                |  |  |

| 5       | RDATA          | TS OP | C-BUS: A 3-state C-BUS serial data output to the $\mu$ C. This output is high impedance when not sending data to the $\mu$ C.                                                                                                                                |  |  |

| 6       | SCLK           | IP    | C-BUS: The C-BUS serial clock input from the $\mu$ C.                                                                                                                                                                                                        |  |  |

| 7       | CDATA          | IP    | C-BUS: Serial data input from the $\mu$ C.                                                                                                                                                                                                                   |  |  |

| 8       | CSN            | IP    | C-BUS: The C-BUS chip select input from the $\mu C$ - there is no internal pullup on this input.                                                                                                                                                             |  |  |

| 9       | DVDD           | PWR   | The 3.3V positive supply rail for the digital on-chip circuits. This pin should be decoupled to DVSS by capacitors mounted close to the device pins.                                                                                                         |  |  |

| 10      | XTAL/CLOCK     | IP    | Input to the oscillator inverter from the Xtal circuit or external clock source.                                                                                                                                                                             |  |  |

| 11      | XTALN          | OP    | The output of the on-chip Xtal oscillator inverter.                                                                                                                                                                                                          |  |  |

| 12      | DVSS           | PWR   | Digital ground.                                                                                                                                                                                                                                              |  |  |

| 13      | MOD            | OP    | Modulator output.                                                                                                                                                                                                                                            |  |  |

| 14      | MICFB          | OP    | MIC input amplifier feedback.                                                                                                                                                                                                                                |  |  |

| 15      | MICN           | IP    | MIC inverting input.                                                                                                                                                                                                                                         |  |  |

| 16      | MICP           | IP    | MIC non-inverting input.                                                                                                                                                                                                                                     |  |  |

| 17      | AVDD           | PWR   | Positive 3.3V supply rail for the analogue on-chip circuits. Levels and thresholds within the device are proportional to this voltage. This pin should be decoupled to AVSS by capacitors mounted close to the device pins.                                  |  |  |

| 18      | AUXADC         | IP    | Auxiliary ADC input (inverted).                                                                                                                                                                                                                              |  |  |

| 19      | VBIAS          | OP    | Internally generated bias voltage of about $AV_{DD}/2$ , except when the device is in 'Powersave' mode when VBIAS pin will discharge to $AV_{SS}$ . Must be decoupled to AVSS by a capacitor mounted close to the device pins. No other connections allowed. |  |  |

| 20      | DISCN2         | IP    | DISC inverting input 2.                                                                                                                                                                                                                                      |  |  |

| 21      | DISCN1         | IP    | DISC inverting input 1.                                                                                                                                                                                                                                      |  |  |

| 22      | DISCFB         | OP    | DISC input amplifier feedback.                                                                                                                                                                                                                               |  |  |

| 23      | AUDIO          | OP    | Audio output.                                                                                                                                                                                                                                                |  |  |

| 24      | AVSS           | PWR   | Analogue ground.                                                                                                                                                                                                                                             |  |  |

| 25      | AUXDAC         | OP    | Auxiliary DAC output/RAMDAC.                                                                                                                                                                                                                                 |  |  |

| 26      | DVSS           | PWR   | Digital ground.                                                                                                                                                                                                                                              |  |  |

CMX138A

| CMX138A | Signal<br>Name | Туре                                                      | Description                             |  |

|---------|----------------|-----------------------------------------------------------|-----------------------------------------|--|

| 27      | CLKSEL         | IP+PU Clock speed select (hi = 6.144MHz, lo = 3.6864MHz). |                                         |  |

| 28      | RXENA          | OP                                                        | Digital output pin – RxENA (active lo). |  |

Notes: IP Input (+ PU/PD = internal pullup/pulldown resistor) = OP Output = BI Bidirectional = TS OP = 3-state Output PWR = Power Connection NC No Connection - should NOT be connected to any signal. =

# 4.1 Signal Definitions

## Table 1 Definition of Power Supply and Reference Voltages

| Signal<br>Name    | Pins  | Usage                                                                           |

|-------------------|-------|---------------------------------------------------------------------------------|

| AV <sub>DD</sub>  | AVDD  | Power supply for analogue circuits                                              |

| DV <sub>DD</sub>  | DVDD  | Power supply for digital circuits                                               |

| V <sub>DEC</sub>  | VDEC  | Power supply for core logic, derived from DV <sub>DD</sub> by on-chip regulator |

| V <sub>BIAS</sub> | VBIAS | Internal analogue reference level, derived from AV <sub>DD</sub>                |

| AV <sub>SS</sub>  | AVSS  | Ground for all analogue circuits                                                |

| DV <sub>SS</sub>  | DVSS  | Ground for all digital circuits                                                 |

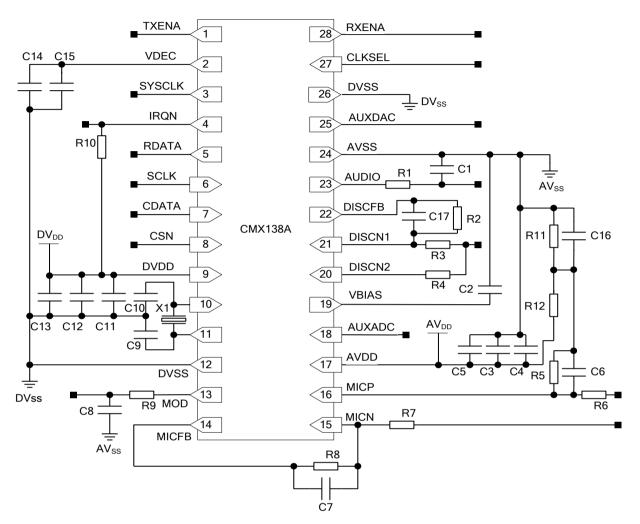

# 5 External Components

## Figure 2 CMX138A Recommended External Components

| R1 | See note 3    | R8  | 100kΩ        | C1 | See note 3 | C9  | 39pF  |

|----|---------------|-----|--------------|----|------------|-----|-------|

| R2 | 100k $\Omega$ | R9  | See note 3   | C2 | 100nF      | C10 | 39pF  |

| R3 | 100kΩ         | R10 | 10kΩ         | C3 | 10µF       | C11 | 10µF  |

| R4 | 100kΩ         | R11 | 10kΩ         | C4 | 10nF       | C12 | 10nF  |

| R5 | 100kΩ         | R12 | $10 k\Omega$ | C5 | 10nF       | C13 | 10nF  |

| R6 | 100kΩ         |     |              | C6 | 100pF      | C14 | 10µF  |

| R7 | 100kΩ         |     |              | C7 | 100pF      | C15 | 10nF  |

|    |               |     |              | C8 | See note 3 | C16 | 100nF |

| X1 | 6.144MHz      |     |              |    |            | C17 | 100pF |

|    | See note 1    |     |              |    |            |     |       |

Resistors  $\pm 5\%$ , capacitors and inductors  $\pm 20\%$  unless otherwise stated.

Notes:

1 X1 can be a crystal or an external clock generator; this will depend on the application. The tracks between the crystal and the device pins should be as short as possible to achieve maximum stability and best start up performance.

<sup>© 2014</sup> CML Microsystems PIc

2 R2 and R3 should be selected to provide the desired dc gain of the discriminator input, as follows:

$$|\text{GAIN}_{\text{DISC}}| = \text{R2} / \text{R3}$$

The gain should be such that the resultant output at the DISCFB pin is within the discriminator input signal range specified in 7.11.2. If the DISCN2 pin is selected the gain becomes:

$$|\text{GAIN}_{\text{DISC}}| = \text{R2} / (\text{R3}//\text{R4})$$

(assuming that R3 and R4 are both connected to the same input signal).

3 R5, R6, R7 and R8 should be selected to provide the desired dc gain of the microphone input.

The gain should be such that the resultant output at the MICFB pin is within the microphone input signal range specified in 7.11.1. For optimum performance with low signal microphones, an additional external gain stage may be required. C6 and C7 should be chosen to maintain a flat low pass response up to 3kHz.

If a single-ended microphone is used, then R6 should be connected to  $V_{BIAS}$  and R5 deleted.

R1 and C1 should be chosen to maintain a flat low pass response up to 3kHz.

R9 and C8 should be chosen to maintain a flat low pass response up to 3kHz.

- 4 If the DISC input is ac coupled, the selection of the coupling capacitor should allow for frequencies from below 50Hz and up to 3kHz to be passed without significant distortion to allow both Audio and sub-audio decoders to function within their specification.

- 5 If the MIC input is dc coupled, the selection of the coupling capacitor should allow for frequencies from 300Hz and up to 3kHz to be passed without significant distortion to allow the audio filtering and processing to function within their specification.

CMX138A

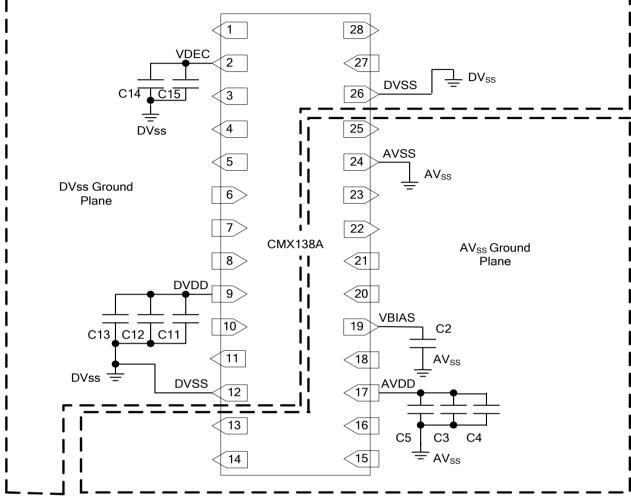

# 5.1 PCB Layout Guidelines and Power Supply Decoupling

Figure 3 CMX138A Power Supply Connections and De-coupling

## Notes:

- 1. It is important to protect the analogue pins from extraneous in-band noise and to minimise the impedance between the device and the supply and bias de-coupling capacitors. The de-coupling capacitors should be as close as possible to the device. It is therefore recommended that the printed circuit board is laid out with separate ground planes for the AV<sub>SS</sub>, and DV<sub>SS</sub> supplies in the area of the CMX138A, with provision to make links between them, close to the device. Use of a multi-layer printed circuit board will facilitate the provision of ground planes on separate layers.

- V<sub>BIAS</sub> is used as an internal reference for detecting and generating the various analogue signals. It

must be carefully decoupled, to ensure its integrity, so apart from the decoupling capacitor shown, no

other loads should be connected. If V<sub>BIAS</sub> needs to be used to set the discriminator mid-point

reference, it must be buffered with a high input-impedance buffer.

## 6 General Description

The CMX138A is intended for use in half duplex analogue two way mobile radio or family radio equipment and is particularly suited to enhanced MURS/GMRS/FRS designs. The CMX138A provides a user programmable frequency inversion audio scrambler integrated with signal processing functions, CTCSS, DCS and in-band tones, permitting sophisticated levels of tone control and voice processing. A flexible power control facility allows the device to be placed in its optimum powersave mode when not actively processing signals.

The CMX138A includes a crystal clock generator, with buffered output, to provide a common system clock if required. A block diagram of the CMX138A is shown in Figure 1.

The signal processing blocks are assigned to particular inputs/outputs. A facility to completely bypass the device is provided (with programmable gain).

## Tx functions:

- o Single microphone input with input amplifier, programmable gain adjust and AGC

- Filtering selectable for 12.5kHz and 25kHz channels

- Selectable pre-emphasis

- Selectable compression

- Selectable frequency inversion voice scrambling

- Programmable scrambler inversion frequency

- Selectable audio processing order

- Single-point modulation outputs with programmable level adjustment

- Pre-programmed 51-tone CTCSS encoder

- 180 degree CTCSS phase shift generation

- Programmable 23/24-bit DCS encoder

- Programmable In-band Tone generator

- Programmable audio tone generator (for custom audio tones)

#### **Rx functions:**

- Demodulator input with input amplifier and programmable gain adjustment

- o Audio-band and sub-audio rejection filtering

- o Selectable de-emphasis

- Selectable expansion

- Selectable frequency inversion voice de-scrambling

- o Programmable scrambler inversion frequency

- Selectable audio processing order

- Software volume control

- o 1 from 51 CTCSS decoder + Tone Clone™ mode

- o 23/24-bit DCS decoder

- In-band Tone decoder

## Auxiliary functions:

© 2014 CML Microsystems Plc

- Programmable system clock output

- Auxiliary ADC

- o Auxiliary DAC, with built-in programmable RAMDAC

- Selectable default Xtal options, 6.144MHz or 3.6864MHz

#### Interface:

- C-BUS: 4-wire high speed synchronous serial command/data bus

- Open drain IRQ to host

- Two Output Enable pins

# 7 Detailed Descriptions

## 7.1 Xtal Frequency

The CMX138A is designed to work with a Xtal or external frequency source of 6.144MHz or 3.6864MHz (as selected by the state of the CLKSEL pin). If either of these default configurations is not suitable, then Program Register Block 3 should to be loaded with the correct values to ensure that the device will work to specification with the user specified clock frequency. A table of common values can be found in Table 2. Note the maximum Xtal frequency is 12.288MHz, although an external clock source of up to 24.576MHz can be used.

The register values in Table 2 are shown in hex (however only the lower 10 bits are relevant), the default settings are shown in bold, and the settings which do not give an exact setting (but are within acceptable limits) are in italics. The new P3.2-3 settings take effect following the write to P3.3 (the settings in P3.4-7 are implemented on a change to Rx or Tx mode). Check that the PRG flag is set in the Status register (\$C6 bit 0 is set to '1') before writing each new P3.2 – P3.7 value via the Programming register (\$C8). If a default frequency is not used, the register values in Table 2 should be programmed into the CMX138A immediately after power-up.

| Program Register |       |                                     | Program Register External frequency source (MHz) |           |                    |         |         |         |         |         |         |

|------------------|-------|-------------------------------------|--------------------------------------------------|-----------|--------------------|---------|---------|---------|---------|---------|---------|

|                  |       |                                     | 3.579                                            | 3.6864    | 6.144              | 9.0592  | 12.0    | 12.8    | 16.368  | 16.8    | 19.2    |

| P3.2             | 0     | GP Timer                            | \$017                                            | \$017     | \$018              | \$018   | \$019   | \$019   | \$018   | \$019   | \$018   |

| P3.3             | Idle  | VCO output<br>and AUX clk<br>divide | \$085                                            | \$085     | \$088              | \$10F   | \$10F   | \$110   | \$095   | \$115   | \$099   |

| P3.4             |       | Ref clk divide                      | \$043                                            | \$024     | \$040              | \$0C6   | \$07D   | \$0C8   | \$155   | \$15E   | \$0C8   |

| P3.5             | Tx    | PLL clk divide                      | \$398                                            | \$1E0     | \$200              | \$370   | \$200   | \$300   | \$400   | \$400   | \$200   |

| P3.6             | Rx or | VCO output<br>and AUX clk<br>divide | \$140                                            | \$140     | \$140              | \$140   | \$140   | \$140   | \$140   | \$140   | \$140   |

| P3.7             |       | Internal ADC /<br>DAC clk divide    | \$008                                            | \$008     | \$008              | \$008   | \$008   | \$008   | \$008   | \$008   | \$008   |

| Con              | nect  | CLKSEL pin to:                      | $DV_{SS}$                                        | $DV_{SS}$ | $\mathbf{DV}_{DD}$ | $DV_DD$ | $DV_DD$ | $DV_DD$ | $DV_DD$ | $DV_DD$ | $DV_DD$ |

Table 2 Xtal/clock Frequency Settings for Program Block 3

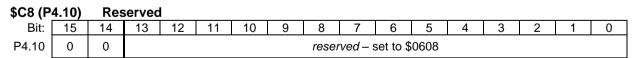

## 7.2 Host Interface

A serial data interface (C-BUS) is used for command, status and data transfers between the CMX138A and the host  $\mu$ C; this interface is compatible with microwire, SPI. Interrupt signals notify the host  $\mu$ C when a change in status has occurred and the  $\mu$ C should read the status register across the C-BUS and respond accordingly. Interrupts only occur if the appropriate mask bit has been set. See section 8.1.1.

The device will monitor the state of the C-BUS registers that the host has written to every 250µs (the C-BUS latency period) hence it is not advisable for the host to make successive writes to the <u>same</u> C-BUS register within this period.

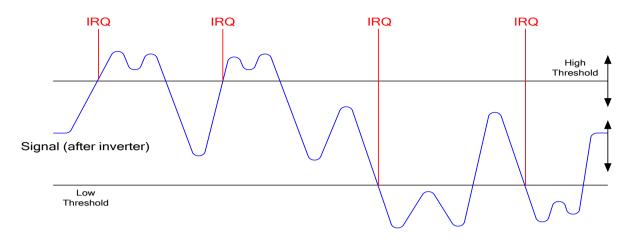

To minimise activity on the C-BUS interface, optimise response times and ensure reliable data transfers, it is advised that the IRQ facility be utilised (using the IRQ mask register, \$CE). It is permissible for the host to poll the IRQ pin if the host uC does not support a fully interrupt-driven architecture. This removes the need to continually poll the C-BUS status register (\$C6) for status changes.

## 7.2.1 C-BUS Operation

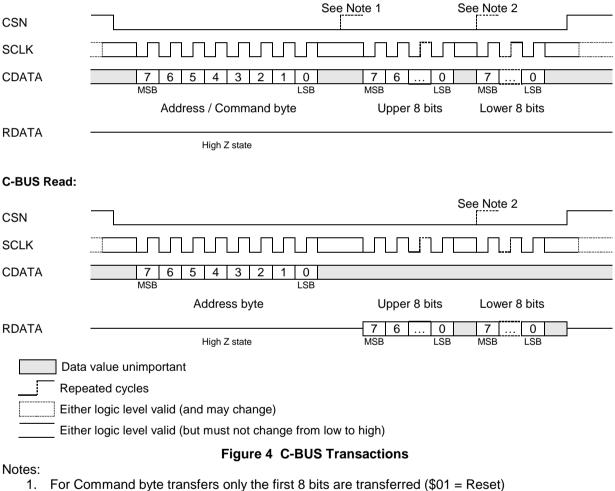

This block provides for the transfer of data and control or status information between the CMX138A's internal registers and the host  $\mu$ C over the C-BUS serial interface. Each transaction consists of a single

Address byte sent from the  $\mu$ C which may be followed by one or more Data byte(s) sent from the  $\mu$ C to be written into one of the CMX138A's Write Only registers, or one or more data byte(s) read out from one of the CMX138A's Read Only registers, as illustrated in Figure 4.

Data sent from the  $\mu$ C on the CDATA line is clocked into the CMX138A on the rising edge of the SCLK input. RData sent from the CMX138A to the  $\mu$ C is valid when the SCLK is high. The CSN line must be held low during a data transfer and kept high between transfers. The C-BUS interface is compatible with most common  $\mu$ C serial interfaces and may also be easily implemented with general purpose  $\mu$ C I/O pins controlled by a simple software routine.

The number of data bytes following an Address byte is dependent on the value of the Address byte. The most significant bit of the address or data are sent first. For detailed timings see section 11.2. Note that, due to internal timing constraints, there may be a delay of up to 250µs between the end of a C-BUS write operation and the CMX138A responding to the C-BUS command. Ensure that this C-BUS latency time (up to 250µs) is observed when writing multiple commands to the same C-BUS register.

#### C-BUS Write:

- 2. For single byte data transfers only the first 8 bits of the data are transferred

- 3. The CDATA and RDATA lines are never active at the same time. The Address byte determines the data direction for each C-BUS transfer.

- 4. The SCLK input can be high or low at the start and end of each C-BUS transaction

- 5. The gaps shown between each byte on the CDATA and RDATA lines in the above diagram are optional, the host may insert gaps or concatenate the data as required.

CMX138A can be set into many modes to suit the environment in which it is to be used. These modes are described in the following sections and are programmed over the C-BUS: either directly to operational registers or, for parameters that are not likely to change during operation, via the Programming register (\$C8).

For basic operation:

- 1. Enable the relevant hardware sections via the Power Down Control register

- 2. Set the appropriate mode registers to the desired state (Audio, In-band, Sub-Audio etc.)

- 3. Select the required Signal Routing and Gain

- 4. Use the Mode Control register to place the device into Rx or Tx mode

To conserve power when the device is not actively processing an analogue signal, place the device into Idle mode. Additional powersaving can be achieved by disabling the unused hardware blocks, however, care must be taken not to disturb any sections that are automatically controlled.

See:

- Power Down Control \$C0 write

- Mode Control \$C1 write

## 7.3.1 Signal Routing

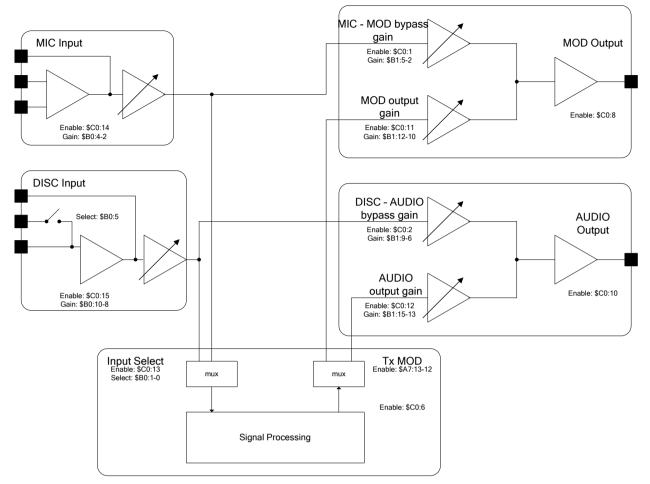

The CMX138A offers a flexible routing architecture, with two signal inputs, a single signal processing path with an optional bypass and both Tx Modulation and Audio outputs. Each of the signalling processing blocks is routed directly to the appropriate input and output blocks.

See:

- Analogue Output Gain \$B1 write

- AuxADC and TX MOD Mode \$A7 write

- $\circ$  Mode Control \$C1 write.

## Figure 5 Signal Routing

The analogue gain/attenuation of each input and output can be set individually, with additional Fine Gain control available via the Programming registers.

See:

- Analogue Input Gain \$B0 write

- Analogue Output Gain \$B1 write

- Audio Tone \$CD: 16-bit write.

## 7.3.2 Mode Control

The CMX138A operates in one of three modes:

- o Idle

- o Rx

- o Tx

At power-on or following a Reset, the device will automatically enter Idle mode, which allows for the maximum powersaving whilst still retaining the capability of monitoring the AuxADC input (if enabled). It is only possible to write to the Programming register whilst in Idle mode.

See:

• Mode Control – \$C1 write.

## 7.4 Audio Functions

The audio signal can be processed in several ways, depending on the implementation required, by selecting the relevant bits in the Audio Control – \$C2 write register. In both Rx and Tx, a selectable channel filter to suit either the 12.5kHz or 25kHz TIA/ETSI channel mask can be selected. This filter also incorporates a selectable hard or soft limiter to reduce the effects of over-modulation. Other features include 300Hz HPF, pre- and de-emphasis, companding and frequency inversion scrambling, all of which may be individually enabled. The order in which these features are executed is selectable to ensure compatibility with existing implementations and provide optimal performance (see section 9.2.5).

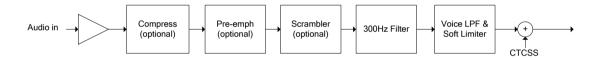

## 7.4.1 Audio Receive Mode

The CMX138A operates in half duplex, so whilst in receive mode the transmit path (microphone input and modulator output amplifiers) can be disabled and powered down. The audio output signal level is equalised (to  $V_{BIAS}$ ) before switching between the audio port and the modulator ports, to minimise unwanted audible transients. In the powersave state, the audio output pin enters a hi-Z state, however, if left enabled and the preceding stages powersaved, it will be driven to the V<sub>BIAS</sub> level.

See:

• Audio Control – \$C2 write.

## Receiving Audio Band Signals

When a voice-based signal is being received, it is up to the host  $\mu$ C, in response to signal status information provided by the CMX138A, to control muting/enabling of the audio signal to the AUDIO output.

The discriminator path through the device has a programmable gain stage. Whilst in receive mode this should normally be set to 0dB (the default) gain.

#### **Receive Filtering**

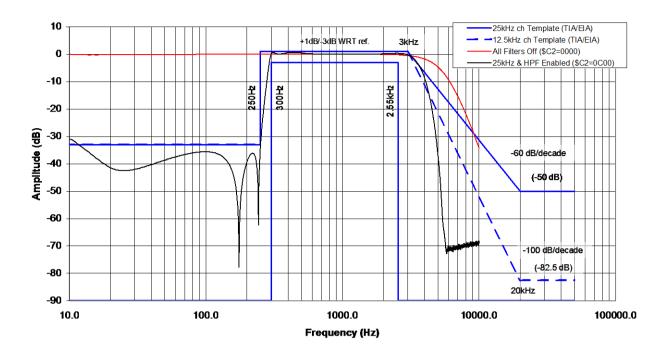

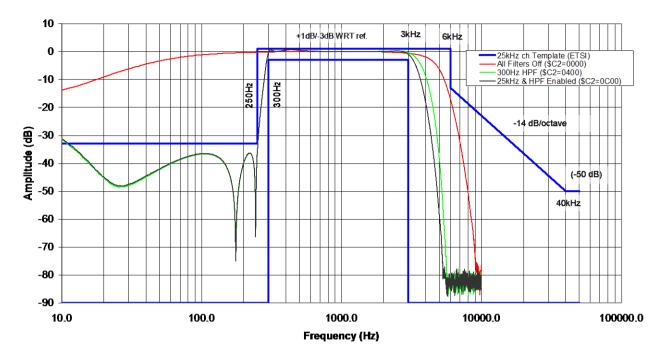

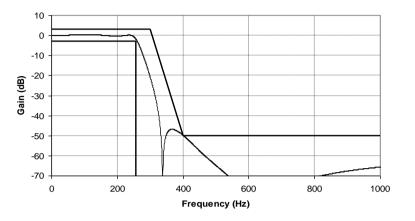

The incoming signal is filtered, as shown in Figure 6 (with the 300Hz HPF also active), to remove subaudio components and to minimise high frequency noise. When appropriate, the audio signal can then be routed to the AUDIO output. Separate selectable filters are available for:

- 300Hz High Pass (to reject sub-audible signalling)

- 2.55kHz Low Pass (for 12.5kHz channel operation)

- 3.0kHz Low Pass (for 25kHz channel operation)

Note that with <u>no</u> filters selected, the low frequency response extends to below 5Hz at the low end but still rolls off above 3.3kHz at the top end.

Figure 6 Rx 25kHz Channel Audio Filter Frequency Response

Figure 7 De-emphasis Curve for TIA/EIA-603 Compliance

## De-emphasis

Optional de-emphasis at -6dB per octave from 300Hz to 3000Hz (shown in Figure 7) can be selected, to facilitate compliance with TIA/EIA-603, EN 300 086, EN 301 025 etc. The template shows the +1, -3dB limits.

## Rx Companding (Expanding)

The CMX138A incorporates an optional syllabic compandor in both transmit and receive modes. This expands received audio band signals that have been similarly compressed in the transmitter to enhance dynamic range. See section 7.4.3 and:

$\circ$  Audio Control – \$C2 write.

#### Audio De-scrambling

The CMX138A incorporates an optional frequency inversion de-scrambler in receive mode. This descrambles received audio band signals that have been scrambled in the transmitter. The inversion frequency can be programmed using the Scramble Frequency register, \$CB. The default value is 3300Hz.

See:

- $\circ$  Audio Control \$C2 write

- Scrambler Inversion Frequency \$CB write.

#### 7.4.2 Audio Transmit Mode

The device operates in half duplex, so when the device is in transmit mode the receive path (discriminator and audio output amplifiers) should be disabled, and can be powered down, by the host  $\mu$ C.

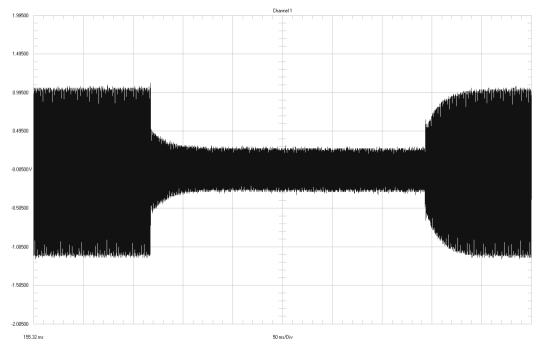

A single modulator output with programmable gain is provided which combines both the audio and subaudio signals to facilitate single or two-point modulation.

To avoid spurious transmissions when changing from Rx to Tx the MOD output is ramped to the quiescent modulator output level,  $V_{BIAS}$  before switching. Similarly, when starting a transmission, the transmitted signal is ramped up from the quiescent  $V_{BIAS}$  level and when ending a transmission the transmitted signal is ramped down to the quiescent  $V_{BIAS}$  level. The ramp rates are set in the Programming register P4.6 and enabled by bits 0,1 of the Analogue Input Gain register. When the modulator output is disabled, their outputs will be set to  $V_{BIAS}$ . When the modulator output driver is powered down, its output will enter a hi-Z state (high impedance), so the external RF modulator should be disabled to avoid unwanted transmissions.

For all transmissions, the host  $\mu$ C must only enable signals after the appropriate data and settings for those signals are loaded into the C-BUS registers. As soon as any signalling is enabled the CMX138A will use the settings to control the way information is transmitted.

A programmable gain stage in the microphone input path facilitates a host controlled VOGAD capability.

See:

- Audio Control \$C2 write

- Analogue Input Gain \$B0 write.

## Processing Audio Signals for Transmission over Analogue Channels

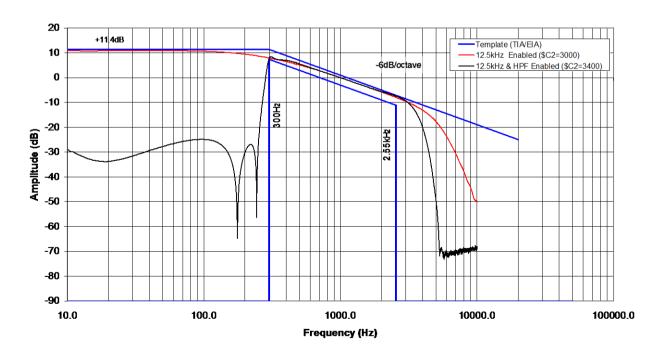

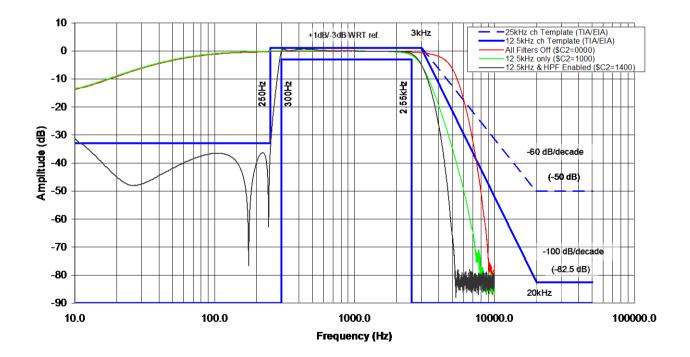

The microphone input, with programmable gain, can be selected as the audio input source. Pre-emphasis is selectable with either of the two analogue Tx audio filters (for 12.5kHz and 25kHz channel spacing). These are designed for use in EN 300 086, TIA/EIA-603 or EN 301 025 compliant applications. When the 300Hz HPF is enabled, it will attenuate sub-audio frequencies below 250Hz by more than 33dB with respect to the signal level at 1kHz.

These filters, together with a built in limiter, help ensure compliance with EN 300 086 and EN 301 025 (25kHz and 12.5kHz channel spacing) when levels and gain settings are set up correctly in the target system. The channel filters incorporate a soft-limiter function by default, however, should a hard-limiter be required, this can be enabled by setting bit 13 of Program Register P4.9 (see section 9.2.5). The level at which the limiter starts to operate can also be adjusted using Program Register P4.7 (see section 9.2.5).

Figure 8 Tx Channel Audio Filter Response and Template (ETSI)

Figure 9 Tx Channel Audio Filter Response and Template (TIA)

<sup>© 2014</sup> CML Microsystems Plc

The characteristics of the 12.5kHz channel filter fit the template shown in Figure 8 and Figure 9. This filter also facilitates implementation of systems compliant with TIA/EIA-603 'A', 'B' and 'C' bands .

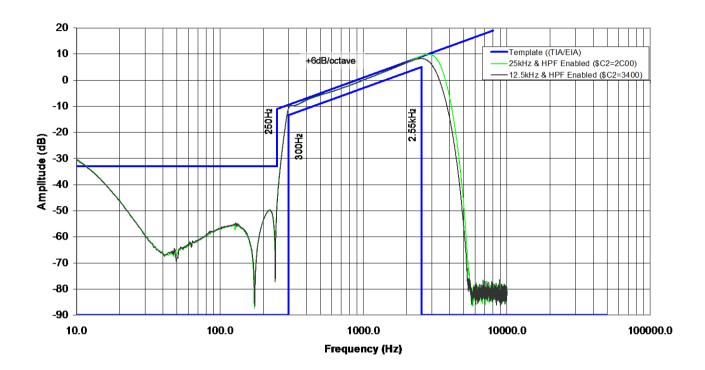

The CMX138A provides selectable pre-emphasis filtering of +6dB per octave from 300Hz to 3000Hz, matching the template shown in Figure 10.

Figure 10 Audio Frequency Pre-emphasis

## Modulator Output Routing

The sub-audio component is combined with the audio band signal and this composite signal routed to the MOD output in accordance with the settings of:

- AuxADC and TX MOD Mode \$A7 write

- Analogue Output Gain \$B1 write

## Input AGC

An Automatic Gain Control system can be enabled by setting the relevant bits of the Program register P4.9. The setting of the Input 1 Gain stage is recorded when the device enters Tx mode and if the signal exceeds the pre-set threshold, the Input 1 Gain is automatically reduced in 3.2dB steps until it falls within the operational levels or the range of the gain stage is exhausted. When the signal level drops, the gain will be automatically increased in 3.2dB steps at the rate set in P4.9 until the initial value has been reached. For maximum effect the system should be designed such that the +22.4dB setting of the Input 1 Gain stage achieves the nominal levels. To ensure consistent operation, it is recommended that the Input 1 Gain stage value be re-initialised before entering Tx mode. The signal that is used as an input to this process can be selected to be either:

- Output of Input1 gain stage

- Output of the Pre-emphasis filter.

by selecting the relevant bit in P4.9. The Pre-emphasis option should only be chosen if this block is actually in use.

<sup>© 2014</sup> CML Microsystems Plc

• Analogue Output Gain - \$B1 writeProgram Block 4 – Gain and Offset Setup:

#### Tx Companding (Compressing)

The CMX138A incorporates an optional syllabic compandor in both transmit and receive mode. This compresses audio band signals before transmission to enhance dynamic range. See section 7.4.3 and:

• Audio Control – \$C2 write.

#### Audio Scrambling

The CMX138A incorporates an optional frequency inversion scrambler in transmit and receive modes. This scrambles transmitted audio band signals, which can then be de-scrambled in the receiver. The inversion frequency can be programmed using the Scramble Frequency register, \$CB. The default value is 3300Hz. The scrambler frequency may be changed while the device is in an active Rx or Tx mode.

See:

- Audio Control \$C2 write

- Scrambler Inversion Frequency \$CB write

## 7.4.3 Audio Compandor

The compandor is comprised of a compressor and an expandor. The compressor's function is to reduce the dynamic range of a given signal by attenuating larger amplitudes while amplifying smaller amplitudes. The expandor's function is to expand the dynamic range of a given signal by attenuating small amplitude signals (e.g. noise) while amplifying large amplitude signals. The compressor is used prior to transmission and the expandor is used in the receiver. Hence, using a compandor will enhance performance in a communication system by transmitting a compressed signal, which is less likely to be corrupted by noise, and then at the receiver expanding the compressed signal, which will push the noise picked up during transmission down further.

The CMX138A uses a "syllabic compandor." This type of compandor, as opposed to the instantaneous compandor (e.g.  $\mu$ /A-law PCM), responds to changes in the average envelope of the signal amplitude according to a syllabic time constant  $\tau$ . Typically, the steady state output for the compressor is proportional to the square root of the input signal, i.e. for a 2 dB change in input signal, the output change will be 1 dB. Generally for voice communication systems a compressor is expected to have an input dynamic range of 60 dB, providing an output dynamic range of 30 dB. The expandor does the inverse.

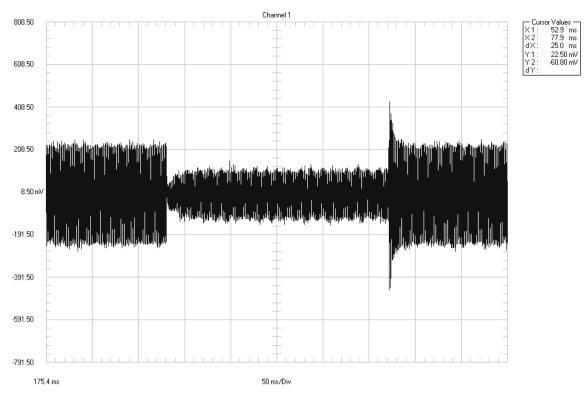

Figure 11 Expandor Transient Response

Figure 12 Compressor Transient Response

## 7.5 Sub-audio Signalling

Sub-audio signalling is available in the audio band below 260Hz. When sub-audio signalling is enabled, the 300Hz HPF in the audio section should also be enabled to remove the sub-audio signalling from the audio signal (in both Tx and Rx). Both CTCSS tones and DCS codes are supported, as well as a special Tone Clone<sup>™</sup> mode which will report back any received CTCSS tone rather than look for a specific tone. There are 51 CTCSS tones defined in the CMX138A and there is provision for a user-specified tone. In Tx only, tone phase adjustment (180 or 120 degrees) to implement "Reverse Tone Burst" for squelch tail elimination can be accomplished by setting b9, b8 of the Audio Control register, \$C2.

The DCS coder/decoder supports both 23- and 24-bit modes with both true and inverse modulation formats and the 134Hz end of transmission burst.

The CTCSS tone and DCS code values for both Rx and Tx operation are specified in the Audio Control register (\$C2), in the lowest 8 bits (shown in decimal):

| 0 | 0          | No tone                                            |

|---|------------|----------------------------------------------------|

| 0 | 1 to 83    | DCS code 1 to 83                                   |

| 0 | 84         | User-defined DCS code                              |

| 0 | 101 to 183 | Inverted DCS code 1 to 83                          |

| 0 | 184        | Inverted user-defined DCS code                     |

| 0 | 200        | CTCSS Tone Clone™ mode                             |

| 0 | 201 to 254 | CTCSS tones 1 to 51, User, XTCSS and DCS off tones |

| 0 | 255        | Invalid tone.                                      |

|   |            |                                                    |

These are detailed in Table 3. The inverted DCS codes are shown in the grey section of the table.

The CTCSS and DCS functions are enabled by the relevant bits in the Mode Control register, \$C1, so that the host can turn the functionality on or off without having to re-program the values in the Audio Control register, \$C2.

#### See:

- o Analogue Input Gain \$B0 write

- Mode Control \$C1 write

- Audio Control \$C2 write.

|         |     |         | DCS and | Invert | ed DCS Code | s       |     |           | (       | TCSS | Tones      |

|---------|-----|---------|---------|--------|-------------|---------|-----|-----------|---------|------|------------|

| Decimal | HEX | data    | Decimal | HEX    | data        | Decimal | HEX | data      | Decimal | HEX  | data       |

| 0       | 000 | No Tone | 64      | 040    | 532         | 128     | 080 | 172       | 192     | 0C0  | Х          |

| 1       | 001 | 023     | 65      | 041    | 546         | 129     | 081 | 174       | 193     | 0C1  | Х          |

| 2       | 002 | 025     | 66      | 042    | 565         | 130     | 082 | 205       | 194     | 0C2  | Х          |

| 3       | 003 | 026     | 67      | 043    | 606         | 131     | 083 | 223       | 195     | 0C3  | Х          |

| 4       | 004 | 031     | 68      | 044    | 612         | 132     | 084 | 226       | 196     | 0C4  | Х          |

| 5       | 005 | 032     | 69      | 045    | 624         | 133     | 085 | 243       | 197     | 0C5  | Х          |

| 6       | 006 | 043     | 70      | 046    | 627         | 134     | 086 | 244       | 198     | 0C6  | Х          |

| 7       | 007 | 047     | 71      | 047    | 631         | 135     | 087 | 245       | 199     | 0C7  | Х          |

| 8       | 008 | 051     | 72      | 048    | 632         | 136     | 088 | 251       | 200     | 0C8  | Tone Clone |

| 9       | 009 | 054     | 73      | 049    | 654         | 137     | 089 | 261       | 201     | 0C9  | 67         |

| 10      | 00A | 065     | 74      | 04A    | 662         | 138     | 08A | 263       | 202     | 0CA  | 71.9       |

| 11      | 00B | 071     | 75      | 04B    | 664         | 139     | 08B | 265       | 203     | 0CB  | 74.4       |

| 12      | 00C | 072     | 76      | 04C    | 703         | 140     | 08C | 271       | 204     | 0CC  | 77         |

| 13      | 00D | 073     | 77      | 04D    | 712         | 141     | 08D | 306       | 205     | 0CD  | 79.7       |

| 14      | 00E | 074     | 78      | 04E    | 723         | 142     | 08E | 311       | 206     | 0CE  | 82.5       |

| 15      | 00F | 114     | 79      | 04F    | 731         | 143     | 08F | 315       | 207     | 0CF  | 85.4       |

| 16      | 010 | 115     | 80      | 050    | 732         | 144     | 090 | 331       | 208     | 0D0  | 88.5       |

| 17      | 011 | 116     | 81      | 051    | 734         | 145     | 091 | 343       | 209     | 0D1  | 91.5       |

| 18      | 012 | 125     | 82      | 052    | 743         | 146     | 092 | 346       | 210     | 0D2  | 94.8       |

| 19      | 013 | 131     | 83      | 053    | 754         | 147     | 093 | 351       | 211     | 0D3  | 97.4       |

| 20      | 014 | 132     | 84      | 054    | User Code   | 148     | 094 | 364       | 212     | 0D4  | 100        |

| 21      | 015 | 134     | 85      | 055    | Х           | 149     | 095 | 365       | 213     | 0D5  | 103.5      |

| 22      | 016 | 143     | 86      | 056    | Х           | 150     | 096 | 371       | 214     | 0D6  | 107.2      |

| 23      | 017 | 152     | 87      | 057    | X           | 151     | 097 | 411       | 215     | 0D7  | 110.9      |

| 24      | 018 | 155     | 88      | 058    | X           | 152     | 098 | 412       | 216     | 0D8  | 114.8      |

| 25      | 019 | 156     | 89      | 059    | X           | 153     | 099 | 413       | 217     | 0D9  | 118.8      |

| 26      | 01A | 162     | 90      | 05A    | X           | 154     | 09A | 423       | 218     | 0DA  | 123        |

| 27      | 01B | 165     | 91      | 05B    | X           | 155     | 09B | 431       | 219     | 0DB  | 127.3      |

| 28      | 01C | 172     | 92      | 05C    | X           | 156     | 09C | 432       | 220     | 0DC  | 131.8      |

| 29      | 01D | 174     | 93      | 05D    | X           | 157     | 09D | 445       | 221     | 0DD  | 136.5      |

| 30      | 01E | 205     | 94      | 05E    | X           | 158     | 09E | 464       | 222     | 0DE  | 141.3      |

| 31      | 01F | 223     | 95      | 05F    | X           | 159     | 09F | 465       | 223     | 0DF  | 146.2      |

| 32      | 020 | 226     | 96      | 060    | Х           | 160     | 0A0 | 466       | 224     | 0E0  | 151.4      |

| 33      | 021 | 243     | 97      | 061    | X           | 161     | 0A1 | 503       | 225     | 0E1  | 156.7      |

| 34      | 022 | 244     | 98      | 062    | Х           | 162     | 0A2 | 506       | 226     | 0E2  | 162.2      |

| 35      | 023 | 245     | 99      | 063    | Х           | 163     | 0A3 | 516       | 227     | 0E3  | 167.9      |

| 36      | 024 | 251     | 100     | 064    | Х           | 164     | 0A4 | 532       | 228     | 0E4  | 173.8      |

| 37      | 025 | 261     | 101     | 065    | 023         | 165     | 0A5 | 546       | 229     | 0E5  | 179.9      |

| 38      | 026 | 263     | 102     | 066    | 025         | 166     | 0A6 | 565       | 230     | 0E6  | 186.2      |

| 39      | 027 | 265     | 103     | 067    | 026         | 167     | 0A7 | 606       | 231     | 0E7  | 192.8      |

| 40      | 028 | 271     | 104     | 068    | 031         | 168     | 0A8 | 612       | 232     | 0E8  | 203.5      |

| 41      | 029 | 306     | 105     | 069    | 032         | 169     | 0A9 | 624       | 233     | 0E9  | 210.7      |

| 42      | 02A | 311     | 106     | 06A    | 043         | 170     | 0AA | 627       | 234     | 0EA  | 218.1      |

| 43      | 02B | 315     | 107     | 06B    | 047         | 171     | 0AB | 631       | 235     | 0EB  | 225.7      |

| 44      | 02C | 331     | 108     | 06C    | 051         | 172     | 0AC | 632       | 236     | 0EC  | 233.6      |

| 45      | 02D | 343     | 109     | 06D    | 054         | 173     | 0AD | 654       | 237     | 0ED  | 241.8      |

| 46      | 02E | 346     | 110     | 06E    | 065         | 174     | 0AE | 662       | 238     | 0EE  | 250.3      |

| 47      | 02F | 351     | 111     | 06F    | 071         | 175     | 0AF | 664       | 239     | 0EF  | 69.3       |

| 48      | 030 | 364     | 112     | 070    | 072         | 176     | 0B0 | 703       | 240     | 0F0  | 62.5       |

| 49      | 031 | 365     | 113     | 071    | 073         | 177     | 0B1 | 712       | 241     | 0F1  | 159.8      |

| 50      | 032 | 371     | 114     | 072    | 074         | 178     | 0B2 | 723       | 242     | 0F2  | 165.5      |

| 51      | 033 | 411     | 115     | 073    | 114         | 179     | 0B3 | 731       | 243     | 0F3  | 171.3      |

| 52      | 034 | 412     | 116     | 074    | 115         | 180     | 0B4 | 732       | 244     | 0F4  | 177.3      |

| 53      | 035 | 413     | 117     | 075    | 116         | 181     | 0B5 | 734       | 245     | 0F5  | 183.5      |

| 54      | 036 | 423     | 118     | 076    | 125         | 182     | 0B6 | 743       | 246     | 0F6  | 189.9      |

| 55      | 037 | 431     | 119     | 077    | 131         | 183     | 0B7 | 754       | 247     | 0F7  | 196.6      |

| 56      | 038 | 432     | 120     | 078    | 132         | 184     | 0B8 | User Code | 248     | 0F8  | 199.5      |

| 57      | 039 | 445     | 121     | 079    | 134         | 185     | 0B9 | Х         | 249     | 0F9  | 206.5      |

| 58      | 03A | 464     | 122     | 07A    | 143         | 186     | 0BA | Х         | 250     | 0FA  | 229.1      |

| 59      | 03B | 465     | 123     | 07B    | 152         | 187     | 0BB | Х         | 251     | 0FB  | 254.1      |

| 60      | 03C | 466     | 124     | 07C    | 155         | 188     | 0BC | Х         | 252     | 0FC  | User Tone  |

| 61      | 03D | 503     | 125     | 07D    | 156         | 189     | OBD | X         | 253     | 0FD  | XTCSS      |

|         | 03E | 506     | 126     | 07E    | 162         | 190     | OBE | X         | 254     | OFE  | DCS off    |

| 62      |     |         |         |        |             |         |     |           |         |      |            |

## Table 3 DCS Codes and CTCSS Tones

$\ensuremath{\textcircled{}^{\circ}}$  2014 CML Microsystems PIc

## 7.5.1 Receiving and Decoding CTCSS Tones

The CMX138A is able to accurately detect valid CTCSS tones quickly, to avoid losing the beginning of audio or data transmissions, and is able to continuously monitor the detected tone with minimal probability of falsely dropping out. The received signal is filtered in accordance with the template shown in Figure 13, to prevent signals outside the sub-audio range from interfering with the sub-audio tone detection.

Figure 13 Low Pass Sub-audio Band Filter for CTCSS and DCS

Once a valid CTCSS tone has been detected, Status register (C6) b11 will be set and the host  $\mu$ C can then route the audio band signal to the audio output. The audio band signal is extracted from the received signal by bandpass filtering as shown in Figure 6.

To optimise the CTCSS tone decoder, adjustable decoder bandwidths and threshold levels allow the user to trade-off decode certainty against signal-to-noise performance when congestion or range restrict the system performance. The tone decoder bandwidth and threshold level are set in P2.1 of the Programming register (\$C8) and the desired tone is programmed in the Audio Control register (\$C2). In systems which make use of tones 41 to 51 or other "split" tones (tones in between the frequencies of tones 1 to 40), the CTCSS decoder bandwidth should be reduced to avoid false detection of adjacent tones.

When enabled, an interrupt will be issued when an input signal matching a CTCSS tone in Table 3 changes state (ie: on, off or to or from a different tone). If a sub-audio tone is present, but it is not one of the valid CTCSS tones (as shown in Table 3), then it will be reported as an unrecognised tone. If a tone other than the programmed tone is detected, it will be reported as an Invalid tone, unless Tone Cloning is enabled, in which case it will report the detected tone number. Note that CTCSS phase changes are not detected. If enabled, an IRQ will be generated under the following conditions:

| State change from: | To:               | IRQ | Tone Status value b7-0 |

|--------------------|-------------------|-----|------------------------|

| No Tone            | Own Tone          | yes | Own Tone               |

| Own Tone           | No Tone           | yes | \$00                   |

| No Tone            | Unrecognised Tone | yes | \$FF                   |

| Unrecognised Tone  | No Tone           | yes | \$00                   |

| No Tone            | Invalid Tone      | yes | \$FF or detected Tone  |

| Invalid Tone       | No Tone           | yes | \$00                   |

## Tone Cloning<sup>™</sup>

Tone Cloning<sup>M</sup> facilitates the detection of CTCSS tones 1 to 39 in receive mode which allows the device to non-predictively detect any tone in this range. This mode is activated by programming CTCSS Tone Number 00 (b0-7 of Audio Control register = 200 decimal). The received tone number will be reported in the Tone Status register (\$CC) and can then be programmed into the Audio Control register by the host  $\mu$ C. The cloned tone will only be active when CTCSS is enabled in the Mode Control register (\$C1). This setting has no effect in Tx mode and the CTCSS generator will output no signal.

<sup>&</sup>lt;sup>T</sup>Tone Cloning<sup>™</sup> is a trademark of CML Microsystems Plc.

<sup>© 2014</sup> CML Microsystems Plc

Tone Cloning<sup>™</sup> should not be used in systems where tones 41 to 51 or other "split" tones (tones between the frequencies of tones 1 to 40) may be received. The all-call tone 40 can still be used after Tone Cloning<sup>™</sup> has been performed. The CTCSS decoder detection bandwidth should be set to its lowest value (in P2.1 of the Programming Register) to ensure accurate detection.

## **CTCSS** Tones

Table 3 lists the CTCSS tones available, the tone numbers and the equivalent (decimal) values that need to be programmed into b7-0 of the Audio Control register (\$C2) and which will be reported back in the Tone Status register (\$CC).

Notes

- Register value 00 in b0-7 of the Tone Status register (\$CC) indicates that none of the above subaudio tones is being detected. If register value 00 is programmed into the Audio Control register (\$C2) and CTCSS enabled in the Mode Control register (\$C1), only CTCSS tone 40 (240 decimal) will be scanned for. If CTCSS transmit is selected, this tone setting will cause the CTCSS generator to output no signal.

- 2. Tone number 40 (240 decimal) provides an all-user CTCSS tone option; regardless of the subaudio tones set, the CMX138A will report the presence of this tone whenever the CTCSS detector is enabled. This feature is useful for implementing emergency type calls e.g. All-Call.

- 3. Tone number 55 (255 decimal) is reported in the Tone Status register (\$CC), when CTCSS receive is enabled and a sub-audio tone is detected that does <u>not</u> correspond to the selected tone or the all-call tone (tone number 40). This could be a tone in the sub-audio band which is not in the table or a tone in the table which is not the selected tone or All-Call tone.

- 4. Tones 40 to 51 (240 to 251 decimal) are not in the TIA-603 standard.

- 5. Tone number 52 (252 decimal) will select the User Programmable Tone value in Program Block 2 CTCSS and DCS Setup.

- 6. Tone number 53 (253 decimal) will select the XTCSS call maintenance tone, 64.7Hz.

- 7. Tone number 54 (254 decimal) will select the DCS turn-off tone, 134.4Hz.

- 8. Tone Clone, register value 200, is a write-only value to the Audio Control register (\$C2). It will not be reported back in the Tone Status register (\$CC). Instead, the received tone number is reported back in this register.

## 7.5.2 Receiving and Decoding DCS Codes

DCS code is in NRZ format and transmitted at 134.4±0.4bps. The CMX138A is able to decode any 23- or 24-bit pattern in either of the two DCS modulation modes defined by TIA/EIA-603 and described in Table 4. The CMX138A can detect a valid DCS code quickly enough to avoid losing the beginning of audio transmissions.

| Modulation Type: | Data Bit: | FM Frequency Change:     |

|------------------|-----------|--------------------------|

| A                | 0         | Negative frequency shift |

|                  | 1         | Positive frequency shift |

| В                | 0         | Positive frequency shift |

|                  | 1         | Negative frequency shift |

## Table 4 DCS Modulation Modes

The CMX138A detects the DCS code that matches the programmed code defined in the Audio Control register (\$C2) in either its true or inverted form. Register values 1 to 83 correspond to modulation type A ("true") and register values 101 to 183 correspond to modulation type B ("inverted"). A facility for a user-defined code is available via Program Block 2 – CTCSS and DCS Setup. The signal inversion caused by the input amplifier is automatically compensated for in the device, so that a true DCS signal applied at its input will be decoded as a true code in the Tone Status register (\$CC). Note that monitoring this signal at the DISCFB pin will show an inverted waveform.

To detect the pre-programmed DCS code, the signal is low-pass filtered to suppress all but the sub-audio band, using the filter shown in Figure 13. Further equalisation filtering, signal slicing and level detection are performed to extract the code being received. The extracted code is then matched with the

Den Den

programmed 23- or 24-bit DCS code to be recognised, in the order least significant first through to most significant DCS code bit last. Table 5 shows a selection of valid 23-bit DCS codes: this does not preclude other codes being programmed. Recognition of a valid DCS code will be flagged if the decode is successful (3 or less errors) by setting b10 of the Status register (\$C6) to 1. A failure to decode is indicated by clearing this bit to 0. This bit is updated after the decoding of every 4th bit of the incoming signal. The actual code received is reported back in the Tone Status register (\$CC) according to Table 3, so that the host  $\mu$ C can determine if it was the true or inverted form of the code.

Once a valid DCS code has been detected, the host  $\mu$ C can route the audio band signal to the audio output. The audio signal is extracted from the received input signal by band pass filtering, see Figure 6.

The end of DCS transmissions is indicated by a 134.4  $\pm$ 0.5Hz tone for 150-200ms. When a valid DCS code has been detected, the CMX138A will automatically scan for the turn-off tone. When the DCS turn-off tone is detected it will cause a DCS interrupt and report tone 54 (Tone Status b0-7 value 254 decimal); the receiver audio output can then be muted by the host. Note that, due to the asynchronous nature of the turn-off tone, it is possible for both a "no-tone" and a "turn-off" tone to be indicated at the end of a DCS transmission. Note that DCS detection and CTCSS detection can not be performed concurrently.

| Reg           | Reg             | DCS  | DCS           | DCS          | Reg           | Reg             | DCS  | DCS           | DCS          | Reg           | Reg             | DCS  | DCS           | DCS          |

|---------------|-----------------|------|---------------|--------------|---------------|-----------------|------|---------------|--------------|---------------|-----------------|------|---------------|--------------|

| Value<br>True | Value<br>Invert | Code | bits<br>22-12 | bits<br>11-0 | Value<br>True | Value<br>Invert | Code | bits<br>22-12 | bits<br>11-0 | Value<br>True | Value<br>Invert | Code | bits<br>22-12 | bits<br>11-0 |

| 1             | 101             | 023  | 763           | 813          | 29            | 129             | 174  | 18B           | 87C          | 57            | 157             | 445  | 7B8           | 925          |

| 2             | 102             | 025  | 6B7           | 815          | 30            | 130             | 205  | 6E9           | 885          | 58            | 158             | 464  | 27E           | 934          |

| 3             | 103             | 026  | 65D           | 816          | 31            | 131             | 223  | 68E           | 893          | 59            | 159             | 465  | 60B           | 935          |

| 4             | 104             | 031  | 51F           | 819          | 32            | 132             | 226  | 7B0           | 896          | 60            | 160             | 466  | 6E1           | 936          |

| 5             | 105             | 032  | 5F5           | 81A          | 33            | 133             | 243  | 45B           | 8A3          | 61            | 161             | 503  | 3C6           | 943          |

| 6             | 106             | 043  | 5B6           | 823          | 34            | 134             | 244  | 1FA           | 8A4          | 62            | 162             | 506  | 2F8           | 946          |

| 7             | 107             | 047  | 0FD           | 827          | 35            | 135             | 245  | 58F           | 8A5          | 63            | 163             | 516  | 41B           | 94E          |

| 8             | 108             | 051  | 7CA           | 829          | 36            | 136             | 251  | 627           | 8A9          | 64            | 164             | 532  | 0E3           | 95A          |

| 9             | 109             | 054  | 6F4           | 82C          | 37            | 137             | 261  | 177           | 8B1          | 65            | 165             | 546  | 19E           | 966          |

| 10            | 110             | 065  | 5D1           | 835          | 38            | 138             | 263  | 5E8           | 8B3          | 66            | 166             | 565  | 0C7           | 975          |

| 11            | 111             | 071  | 679           | 839          | 39            | 139             | 265  | 43C           | 8B5          | 67            | 167             | 606  | 5D9           | 986          |

| 12            | 112             | 072  | 693           | 83A          | 40            | 140             | 271  | 794           | 8B9          | 68            | 168             | 612  | 671           | 98A          |

| 13            | 113             | 073  | 2E6           | 83B          | 41            | 141             | 306  | 0CF           | 8C6          | 69            | 169             | 624  | 0F5           | 994          |

| 14            | 114             | 074  | 747           | 83C          | 42            | 142             | 311  | 38D           | 8C9          | 70            | 170             | 627  | 01F           | 997          |

| 15            | 115             | 114  | 35E           | 84C          | 43            | 143             | 315  | 6C6           | 8CD          | 71            | 171             | 631  | 728           | 999          |

| 16            | 116             | 115  | 72B           | 84D          | 44            | 144             | 331  | 23E           | 8D9          | 72            | 172             | 632  | 7C2           | 99A          |

| 17            | 117             | 116  | 7C1           | 84E          | 45            | 145             | 343  | 297           | 8E3          | 73            | 173             | 654  | 4C3           | 9AC          |

| 18            | 118             | 125  | 07B           | 855          | 46            | 146             | 346  | 3A9           | 8E6          | 74            | 174             | 662  | 247           | 9B2          |

| 19            | 119             | 131  | 3D3           | 859          | 47            | 147             | 351  | 0EB           | 8E9          | 75            | 175             | 664  | 393           | 9B4          |

| 20            | 120             | 132  | 339           | 85A          | 48            | 148             | 364  | 685           | 8F4          | 76            | 176             | 703  | 22B           | 9C3          |

| 21            | 121             | 134  | 2ED           | 85C          | 49            | 149             | 365  | 2F0           | 8F5          | 77            | 177             | 712  | 0BD           | 9CA          |

| 22            | 122             | 143  | 37A           | 863          | 50            | 150             | 371  | 158           | 8F9          | 78            | 178             | 723  | 398           | 9D3          |

| 23            | 123             | 152  | 1EC           | 86A          | 51            | 151             | 411  | 776           | 909          | 79            | 179             | 731  | 1E4           | 9D9          |

| 24            | 124             | 155  | 44D           | 86D          | 52            | 152             | 412  | 79C           | 90A          | 80            | 180             | 732  | 10E           | 9DA          |

| 25            | 125             | 156  | 4A7           | 86E          | 53            | 153             | 413  | 3E9           | 90B          | 81            | 181             | 734  | 0DA           | 9DC          |

| 26            | 126             | 162  | 6BC           | 872          | 54            | 154             | 423  | 4B9           | 913          | 82            | 182             | 743  | 14D           | 9E3          |

| 27            | 127             | 165  | 31D           | 875          | 55            | 155             | 431  | 6C5           | 919          | 83            | 183             | 754  | 20F           | 9EC          |

| 28            | 128             | 172  | 05F           | 87A          | 56            | 156             | 432  | 62F           | 91A          | 84            | 184             | U    | ser Defin     | ed           |

#### Table 5 DCS 23 Bit Codes

Notes:

Register value 84 will select the User Programmable DCS code value in Program Block 2 – CTCSS and DCS Setup Register value 184 will select the inverted form of the User Programmable DCS code.

2. Note that the Audio Control register values are shown in decimal.

## 7.5.3 Transmit CTCSS Tone